Federal Aviation Administration William J. Hughes Technical Center Aviation Research Division Atlantic City International Airport New Jersey 08405

# Assurance of Multicore Processors: Limits on Interference Analysis

March 2020 Final report

This document is available to the U.S. public through the National Technical Information Services (NTIS), Springfield, Virginia 22161.

This document is also available from the Federal Aviation Administration William J. Hughes Technical Center at actlibrary.tc.faa.gov.

#### NOTICE

This document is disseminated under the sponsorship of the U.S. Department of Transportation in the interest of information exchange. The U.S. Government assumes no liability for the contents or use thereof. The U.S. Government does not endorse products or manufacturers. Trade or manufacturers' names appear herein solely because they are considered essential to the objective of this report. The findings and conclusions in this report are those of the author(s) and do not necessarily represent the views of the funding agency. This document does not constitute FAA policy. Consult the FAA sponsoring organization listed on the Technical Documentation page as to its use.

This report is available at the Federal Aviation Administration William J. Hughes Technical Center's Full-Text Technical Reports page: <u>actlibrary.tc.faa.gov</u> in Adobe Acrobat portable document format (PDF).

#### **Technical Report Documentation Page**

| Form DOT F 1700.7 (8-72)                                              | Reproduction of completed page authorized      |                                            |

|-----------------------------------------------------------------------|------------------------------------------------|--------------------------------------------|

| 1. Report No.                                                         | 2. Government Accession No.                    | 3. Recipient's Catalog No.                 |

| DOT/FAA/TC-19/24                                                      |                                                |                                            |

| 4. Title and Subtitle                                                 |                                                | 5. Report Date                             |

| ASSURANCE FOR MULTICORE PROC<br>ANALYSIS                              | CESSORS: LIMITS OF INTERFERENCE                | March 2020                                 |

| ANAL I SIS                                                            |                                                | 6. Performing Organization Code            |

|                                                                       |                                                | ANG-E271                                   |

| 7. Author(s)                                                          |                                                | 8. Performing Organization Report No.      |

| Xavier Jean, Laurence H. Mutuel, Romain                               | n Soulat                                       |                                            |

| 9. Performing Organization Name and Address                           |                                                | 10. Work Unit No. (TRAIS)                  |

| Thales ATM                                                            |                                                |                                            |

| 10950 El Monte, Suite 110                                             |                                                | 11. Contract or Grant No.                  |

| Overland Park, KS 66211                                               |                                                | DTFACT-13-D-00008                          |

| 12. Sponsoring Agency Name and Address                                |                                                | 13. Type of Report and Period Covered      |

| Federal Aviation Administration                                       | Final Report                                   |                                            |

| William J. Hughes Technical Center                                    |                                                | 14. Sponsoring Agency Code                 |

| Aviation Research Division                                            |                                                | Barbara Lingberg, AIR-6B4                  |

| Atlantic City International Airport, NJ 08405 15. Supplementary Notes |                                                | Darbara Lingberg, AIK-0D4                  |

| 15. Supplementary Notes                                               |                                                |                                            |

| -                                                                     | enter Aviation Research Division Technical I   | Monitor was Srini Mandalapu.               |

| 16. Abstract                                                          |                                                |                                            |

| This report builds on previous research the                           | at addresses interference issues applied to mu | ulticore processors (MCPs). The previously |

proposed methods to perform interference analysis are organized around a set of assertions that the applicant should be able to defend when interacting with the certification authorities from the standpoint of safety and operations. The three assertions involve the applicant's commitment to a quantified interference penalty, the justification that the committable interference penalty can be trusted, and the justification that the proposed methodology for verification is adequate and feasible. To facilitate the interaction between the applicant and the certification authorities regarding these assertions, six key aspects are developed to support the substantiation of the three proposed assertions; therefore, the proposed methods to perform interference analysis are developed around these six key aspects. The notion of limits to the proposed interference analysis methods is developed by listing conditions under which some of these key aspects might be difficult to fulfill or to be fulfilled, but in an unsatisfying manner. These limits are classified as intrinsic to 1) the methods, 2) the MCP chip they are applied, or 3) the industrial environment. Developing this notion of limits highlighted good properties that the applicant can expect from applying an interference analysis method. The first benefit relates to the determination of interference penalties and the safety arguments substantiating these penalties. The second benefit is the scalability to the equipment's level of criticality and developmental stage. The third benefit is the adjustability with respect to the MCP monitoring and tracing capabilities. The last benefit relates to the adaptability to the industrial context in which multiple actors are involved, each having only partial visibility on the hardware and/or software embedded in the equipment. This report proposes an example of limits to an end-to-end interference analysis method driving test campaigns. This example shows that the question of interference analysis must be considered at an early stage of the computation platform design (i.e., the stage of selection of the MCP). The authors' position is that the question of interference analyses should be considered in guidance material in a way that allows applicants to propose their own methods and defend their argumentation.

| 17. Key Words                                                                                            |                                     | <ol><li>Distribution Statement</li></ol>      |                                                                                                                    |                                   |

|----------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Multicore processors, Safety, Interference, Worst-case execution time, Integrated modular avionics, COTS |                                     | National Technical In<br>Virginia 22161. This | ailable to the U.S. publ<br>nformation Service (N<br>document is also avai<br>ministration William J<br>c.faa.gov. | TIS), Springfield, lable from the |

| 19. Security Classif. (of this report)                                                                   | 20. Security Classif. (of this page | ge)                                           | 21. No. of Pages                                                                                                   | 22. Price                         |

| Unclassified                                                                                             | Unclassified                        |                                               | 47                                                                                                                 |                                   |

### Contents

| 1 | In  | trodu         | ıction1                                                                 |  |

|---|-----|---------------|-------------------------------------------------------------------------|--|

|   | 1.1 | .1 Background |                                                                         |  |

|   | 1.2 | Def           | initions1                                                               |  |

|   | 1.3 | Lite          | erature review (update)                                                 |  |

|   | 1.3 | 3.1           | Status of current guidance                                              |  |

|   | 1.3 | 3.2           | Techniques for interference assessment on MCP                           |  |

|   | 1.3 | 3.3           | Pathological situations sampling on MCP                                 |  |

|   | 1.3 | 3.4           | Programming models for interference reduction, bounding, or elimination |  |

|   | 1.3 | 3.5           | Hardware developments for built-in determinism in MCP4                  |  |

|   | 1.3 | 8.6           | System and module-level design for use of MCP in avionics               |  |

|   | 1.4 | Sco           | pe of the report                                                        |  |

| 2 | Li  | mits          | to interference analysis7                                               |  |

|   | 2.1 | Key           | v aspects of interference analysis7                                     |  |

|   | 2.1 | .1            | Hypotheses conditioning trustworthiness in an interference analysis     |  |

|   | 2.1 | .2            | Range of conclusions from interference analysis                         |  |

|   | 2.1 | .3            | Definition of supported applicative profiles on the MCP9                |  |

|   | 2.1 | .4            | Justification of individual test scenarios                              |  |

|   | 2.1 | .5            | Selection of concurrent tests 10                                        |  |

|   | 2.1 | .6            | Evidence collection                                                     |  |

|   | 2.2 | Cla           | ssification of interference analysis limits10                           |  |

|   | 2.2 | 2.1           | Limits intrinsic to interference analysis methods 11                    |  |

|   | 2.2 | 2.2           | Limits relative to MCP chips                                            |  |

|   | 2.2 | 2.3           | Limits relative to the industrial context                               |  |

|   | 2.3 | Syn           | thesis16                                                                |  |

| 3 | Ap  | oplica        | ntion of proposed method and associated limits16                        |  |

|   | 3.1 | Rep           | presentation of applicative profiles                                    |  |

| 5                                         | Referen | nces                                                     | 34 |

|-------------------------------------------|---------|----------------------------------------------------------|----|

| 4                                         | Conclu  | sions                                                    | 33 |

|                                           | 3.4.2   | Summary of adjustable parameters and stop criteria       | 32 |

|                                           | 3.4.1   | Good properties and limits of this example               | 30 |

|                                           | 3.4 Dis | cussion                                                  | 30 |

|                                           | 3.3.2   | Formalization                                            | 29 |

|                                           | 3.3.1   | Overview                                                 | 28 |

|                                           | 3.3 Qua | ality metrics for hardware testing                       | 28 |

|                                           | 3.2.2   | Formalization                                            | 26 |

|                                           | 3.2.1   | Overview                                                 | 24 |

| ,                                         | 3.2 Con | mbination of test cases for parallel execution on an MCP | 24 |

|                                           | 3.1.4   | Examples                                                 | 22 |

|                                           | 3.1.3   | Formalization                                            | 21 |

| 3.1.2 Building a test population on a CPU |         | 20                                                       |    |

|                                           | 3.1.1   | Overview                                                 | 18 |

# Figures

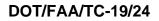

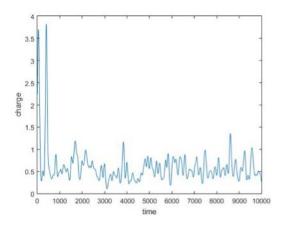

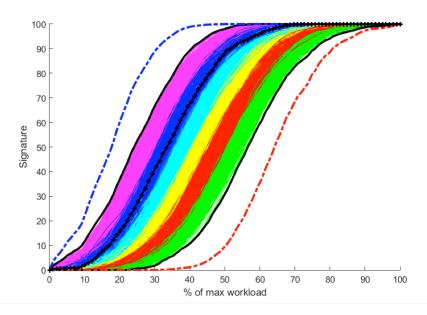

| Figure 1. Simulated example of cumulative repartition curve describing workload on a given                |     |

|-----------------------------------------------------------------------------------------------------------|-----|

| MCP resource                                                                                              | 19  |

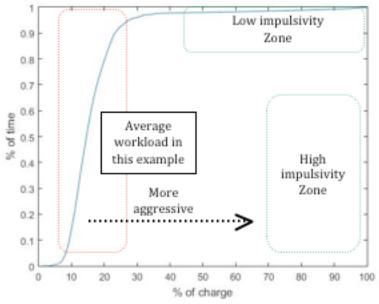

| Figure 2. Example of curves obtained from several simulations of the same application                     | 20  |

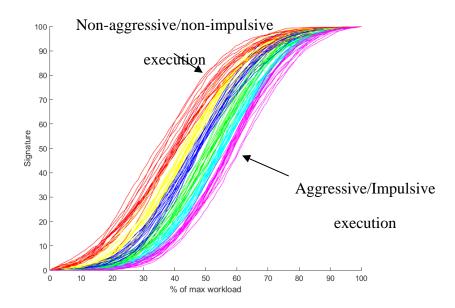

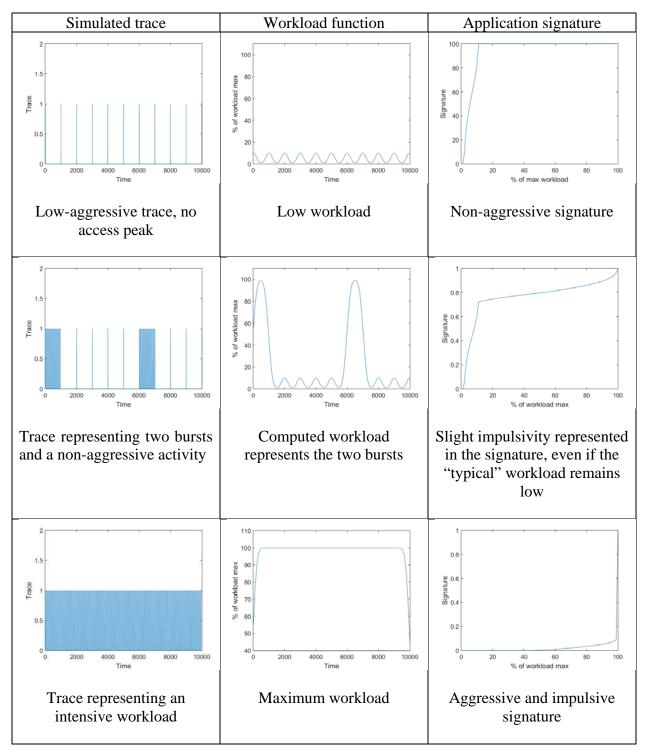

| Figure 3. Example of trace function                                                                       | 22  |

| Figure 4. Workload function computed from trace function                                                  | 22  |

| Figure 5. Signature profile for an aggressive test case                                                   | 25  |

| Figure 6. Signature profile for an aggressive test case                                                   | 25  |

| Figure 7. Signature profile of a regular test case                                                        | 26  |

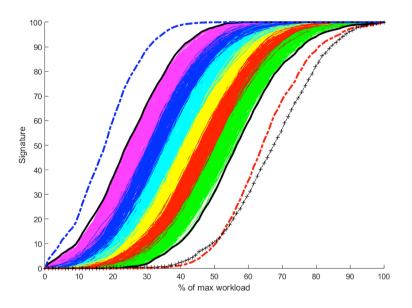

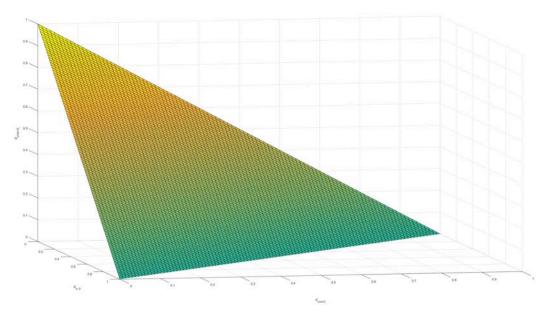

| Figure 8. Representation of the function space to be explored                                             | 27  |

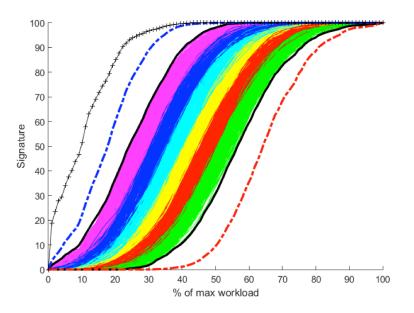

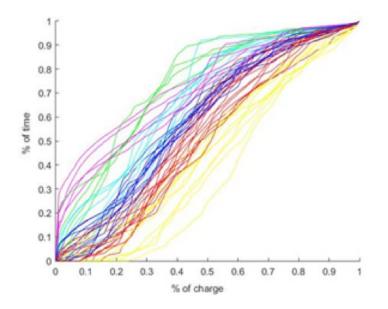

| Figure 9. Example of k- $\epsilon$ dense set of hardware signatures (k=4) "close" colors indicate "close" | se" |

| signatures                                                                                                | 30  |

## Tables

| Table 1. Summary of key aspects and limits of associated methods              | . 11 |

|-------------------------------------------------------------------------------|------|

| Table 2. Summary of key aspect and MCP component relative limits              | . 14 |

| Table 3. Summary of key aspects and limits relative to the industrial context | . 15 |

| Table 4. Examples of computed traces                                          | . 23 |

# Acronyms

| Acronym | Definition                   |  |

|---------|------------------------------|--|

| COTS    | Commercial Off-The-Shelf     |  |

| CPU     | Central Processing Unit      |  |

| DMA     | Direct memory access         |  |

| DoS     | Denial of service            |  |

| DRAM    | Dynamic random access memory |  |

| IMA     | Integrated Modular Avionics  |  |

| I/O     | Input/output                 |  |

| МСР     | Multi Core Processor         |  |

| UD      | Usage Domain                 |  |

| WCET    | Worst-case execution time    |  |

### **Executive summary**

This report builds on previous research that addresses interference issues applied to multicore processors (MCPs). The previously proposed methods to perform interference analysis are organized around a set of assertions that the applicant should be able to defend when interacting with the certification authorities from the standpoint of safety and operations. The three assertions involve the applicant's commitment to a quantified interference penalty, the justification that the committable interference penalty can be trusted, and the justification that the proposed methodology for verification is adequate and feasible.

To facilitate the interaction between the applicant and the certification authorities regarding these assertions, six key aspects were developed to support the substantiation of the three proposed assertions; therefore, the proposed methods to perform interference analysis were developed around these six key aspects:

- The validity of the hypotheses associated with an interference analysis method

- The range of conclusions associated with an interference analysis method

- The scope of supported applicative profiles and combinations of profiles (optional)

- The justification of single-core test cases

- The justification of combinations of test cases for multicore execution

- The collection of evidence and synthesis for the certification authorities

This research focused on the limits to the proposed methods to perform interference analysis. The notion of limits is developed by listing conditions under which some of these key aspects might be difficult to fulfill, or to be fulfilled but in an unsatisfying manner. These limits are classified as intrinsic to 1) the methods, 2) the MCP chip they are applied to, or 3) the industrial environment.

- Limits relative to the interference analysis method point to weaknesses such that additional work on the method is required.

- Limits relative to the MCP component point to weaknesses such that the method or the MCP selection has to be reconsidered.

- Limits relative to the industrial environment point to weaknesses such that the collaboration and information sharing between various actors has to be reconsidered.

Developing this notion of limits highlighted good properties that the applicant can expect from applying an interference analysis method, namely:

- Providing interference penalties to be applied on the software's worst-case execution time and therefore on equipment's performances; and providing safety arguments substantiating these penalties, with good balance between these two objectives.

- Being adjustable according to the equipment's criticality level and developmental stage, especially when these limits are considered at an early developmental stage in which hardware and software building blocks have not achieved a good level of maturity.

- Being adjustable with respect to reachable precision according to the MCP's hardware features, especially the monitoring and tracing capabilities.

- Being adaptable to an industrial context involving multiple industrial actors, each having a partial visibility on hardware and software involved in the equipment. One example of such a context is Integrated Modular Avionics.

This report proposes an example of limits to an end-to-end interference analysis method driving test campaigns. The examples of limits described in each category of key aspects constitute a non-exhaustive list and the selected example does not claim to be universal. Test cases for each processing units might be chosen in various ways, depending or not on targeted applicative profiles. Combinations and execution number of test cases for MCP execution may be proposed differently. Finally, the absence of singularity or other feared event can be argued in other ways. Nonetheless, they show that the question of interference analysis has to be considered at an early stage of the computation platform design (i.e., at the stage of selection of the MCP).

For these reasons, the position of the authors of this report is that the question of interferences analyses should be considered in guidance material in a way that allows applicants to propose their own method and defend their argumentation with very few restrictions, as long as they provide clear answers to fundamental questions, some being developed in this report within the six key aspects.

# 1 Introduction

## 1.1 Background

This report builds on previous research findings that addressed interference issues on multicore processors (MCPs), particularly commercial off-the-shelf (COTS) MCPs for which the avionics suppliers face a high level of complexity on hardware and partial information from their manufacturers.

The notion of interference analysis was defined as a means to assess and justify the penalty to apply on the worst-case execution time (WCET) of the software implemented on one MCP core while other pieces of software are running on the other cores. The method driving the interference analysis must be defined and agreed to by the certification authorities as soon as possible in the certification process. This may be a combination of several methods, involving test campaigns and static analyses of the MCP or subparts of the MCP.

The objective of the interference analysis is twofold. First, it has to provide a realistic interference penalty, which will be taken into account when sizing margins. The challenge is to obtain correct penalties that affect performances. Second, it has to provide safety-related arguments justifying that this interference penalty is trustworthy, so that the impact of the interference analysis can be considered in traditional safety analyses methods.

In the previous report on assurance process for MCPs, examples of techniques for interference analysis, interference reduction, interference bounding, and elimination were presented. This report focuses on interference analysis, whereas other techniques are considered as being design choices made by the platform developer to find the best tradeoff between performances and determinism.

In the previous report [3], the authors argued that principles of Integrated Modular Avionics (IMA) provide a relevant framework for use of MCPs in avionics equipment, even when non-IMA based. Although this research targets all classes of avionics systems, not only IMA systems, IMA terminology is used to distinguish the roles of system integrator that have an overall visibility on the hardware and software and the platform provider who will perform the interference analysis.

## 1.2 Definitions

The following definitions are used in this report:

| Initiator:                | A component of the processor that has the capability to proactively start operations within the shared resources. Examples of initiators are central processing units (CPUs), direct memory access (DMA) engines, master input/output (I/O).                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Target:                   | A component of the processor that can be requested by initiators and either<br>absorbs this activity (e.g., for write operations) or emits its own activity as an<br>answer (e.g., for read operations) to initiator's requests. Examples of targets<br>are memories and slave I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Usage Domain:             | Usage Domain (UD) is the set of constraints defined and mandatorily followed by users to ensure proper behavior of the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Interference:             | Interferences are alterations of the processor's behavior seen by software<br>running on one core due to activities ordered by software running on other<br>cores.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                           | A statement developed in the previous report [3] considers that the impact of interferences is, at first, a problem of performance assessment and timing determinism enforcement. Interferences are undesired phenomena that are considered by the manufacturer as belonging to the functional domain of the processor, but are seen as dysfunctional by the avionics equipment provider, as explained in reference [1].                                                                                                                                                                                                                                                                                                |

| Interference<br>source:   | An interference source is a component on the processor that has simultaneous<br>use by several cores or other initiators that may entail interferences. Examples<br>of interference sources are shared caches and interconnect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Interference<br>path:     | An interference path is a configuration in which a given set of initiators (e.g., cores, DMA engines, master I/O) is allowed to communicate with a given set of targets (e.g., main memory, shared caches, slave I/O) with no restriction. Having an interference path does not necessarily mean interferences will actuallyoccur. It only represents a configuration for which there is a risk of interferences; therefore, interference paths can be seen as test cases in which given initiators are allowed to request given targets (e.g., core 0 targets the main memory while core 1 targets the peripheral component interconnect express (PCIe) controller under which the processor's behavior can be stated. |

| Interference<br>analysis: | An interference analysis is a process that considers interference paths and their usage according to the processor's UD, and determines those that are acceptable (from a performance and safety point of view) and those that are not, which are referred to as interference channels (see definition below).                                                                                                                                                                                                                                                                                                                                                                                                          |

| Interference<br>channel:  | An interference channel is an interference path for which interferences have<br>been actually observed and do not cope with the equipment's functional<br>domain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

## 1.3 Literature review (update)

As a part of the earlier research task on the Assurance of Multicore Processors in Airborne Systems [3], a preliminary literature review [2] was conducted. This section provides a review of the research topics directly and indirectly focusing on interference issues on MCP. This section also presents the key papers discussed earlier in these domains and provides an updated review to the 2015 publication. For a more complete literature review, see reference [2].

### 1.3.1 Status of current guidance

No change has been denoted since 2015 in guidance documents published by certification authorities. The most recent guidance specifically focused on MCPs is the joint CRI-MCP (EASA) and CAST-32 (FAA).

As explained in the final report [3], system-level standards such as SAE ARP4754A [4] and ARP4761 [5] are relevant during the safe design phase for equipment embedding an MCP. The rationale defended in [3] is the intrinsic complexity of MCP, which leads to considering a computing platform as a full system and to referring to system-level guidance. IMA guidance, mostly DO-297 [6], is also a relevant reference for interference issues in MCP, as the robust partitioning aspects may not be satisfied.

Even if they do not constitute an official position of certification authorities, EASA studies Mulcors [7] and COTS-AEH [1] have provided inputs to the certification authorities to develop position papers on the issue.

### 1.3.2 Techniques for interference assessment on MCP

Various interference assessment techniques have been proposed in the literature, most targeting a configuration for which each CPU hosts a single task. Examples of such techniques are as follows:

- Nowotsch [8] proposed a technique called "interference sensitive WCET assessment" using a commercial tool (aiT) to compute an upper bound for competing accesses of concurrent tasks.

- Bin [9-10] introduced the notion of application signature to compute an offline interference penalty for a set of co-running tasks.

- Pellizonni [11] proposed a framework similar to Nowotsch's WCET to assess the interferences on a memory controller.

Several frameworks [12-13] target interference issues on shared caches, especially instruction caches.

- Paolieri [14] modeled a dynamic random access memory (DRAM) controller and computed worst-case delays for incoming requests flows emitted by CPUs.

- Probabilistic works target interferences on MCP. Diaz recently published an example in reference [15].

### 1.3.3 Pathological situations sampling on MCP

Publications in this domain usually document denial-of-service (DoS) attacks on MCPs, benefitting from interferences. Historical publications in this domain were delivered by Nowotsch [16] for DoS on interconnect networks and Moscibroda [17] for DoS on DRAM controllers.

Several works have been recently published on this topic; however, the contributions of Blin [18] for DoS attacks on memory access of benchmarks from the open-source MiBench suite are noteworthy.

### 1.3.4 Programming models for interference reduction, bounding, or elimination

Interference reductions on COTS MCP are obtained by a proper configuration of Quality of Service features when they are available on the MCP (e.g., ARM interconnects) [19].

Software-enforced techniques have been proposed to address interference issues in shared caches and memory controllers. These techniques are called cache coloring [20] and bank partitioning [21], respectively. They are provided within a framework called Single-Core Equivalent Virtual Machines [22].

Girbal described other techniques controlling software execution for enforcement of determinism under the name of Deterministic Platform Software" [23]. An example of a promising technology is the Memguard memory bandwidth regulator [24], which relies on hardware performance counters to limit the concurrent accesses of CPUs to shared resources.

### 1.3.5 Hardware developments for built-in determinism in MCP

Dedicated hardware designs for intrinsic determinism enforcement on MCP have been explored for the past 15 years. This research area led to several prototypes (Merasa, PRET, CompSoC) but none have been industrialized and entered in a long-term production. The question of developing custom MCP remains a current topic in the avionics community.

In the recent studies, the contributions of Hassan can be noted, as detailed in his PhD thesis [30], and summarized in several publications; the interference was focused respectively on arbitration in DRAM controllers [36], cache coherence mechanisms [35] and arbitration policies in interconnect networks [34]. These aspects are known as a major source of non-determinism on MCPs, mostly because of the interferences they can generate.

### 1.3.6 System and module-level design for use of MCP in avionics

Operating system designers who address system designers' needs while dealing with constraints imposed by hardware have customarily addressed this area of research. WindRiver released a white paper [28] detailing some properties of their real-time operating system, particularly regarding interference issues on shared caches and busses. SysGo also contributed to this topic in 2016 [29].

The reference paper from Rushby [30] on robust partitioning issues, although published in 2000, remains relevant with regard to interference issues on MCPs when robust partitioning property is required (e.g., for IMA). A summary of literature regarding robust partitioning is provided in reference [31].

### 1.4 Scope of the report

This report covers the question of limits to the interference analyses. Before the topic of limits can be discussed, more details on interference analyses should be provided. Section 3.1.4 includes examples of techniques that can be useful, but do not constitute solely an interference analysis method.

An interference analysis is driven by applying a dedicated method, which has to be defined by the applicant and agreed to by the certification authorities as soon as possible in the equipment development stage. The authors' position of this report is that test campaigns and offline analyses should be combined to build an interference analysis method. Test campaigns remain central in the proposed approach when dealing with COTS MCP, for which the applicant faces a lack of information disclosed by hardware manufacturers and highly complex chips.

Previous research defined the interference analyses' objectives and placed restrictions on their scope. For instance, the question of interference triggering failure modes on the MCP was excluded to focus on performance and timing determinism issues. Furthermore, stakes were highlighted, mostly dealing with the risk of combinatorial explosions of test campaigns. This report proposes to organize interference analysis methods according to a set of key aspects, detailed in section 2.1. These key aspects are formulated as a set of questions that the applicant

should address independently from the way they should be addressed to ease the interactions between the applicant and the certification authorities for questions relative to interference analysis from a safety and an operational point of view. Limits to interference analyses are developed according to these key aspects.

Informally, these key aspects could help to complete and defend the following assertions:

- 1. Under the following restrictions, I commit on an interference penalty of x%, applied to applicative SW's WCET computed individually.

- 2. I trust this interference penalty because [...].

- 3. I consider my experimental methodology as relevant and feasible because [...].

Assertion 1 is detailed as a key aspect (see section 2.1.3) dealing with supported applicative profiles on the MCP by the platform provider. This key aspect summarizes the kind of constraints applied on applicative software so that the interference analysis can be refined according to these constraints to get tighter, and sometimes realistic, results.

Assertion 2 is refined with two key aspects dealing with safety aspects of interference analyses (see sections 2.1.1 and 2.1.2) and one key aspect dealing with results synthesis and interaction with certification authorities (see section 2.1.6). These key aspects cover the question of interference analyses' trustworthiness hypotheses, conclusion ranges, and evidence collection for synthesis and approval by certification authorities, respectively.

Assertion 3 is refined as two key aspects (see sections 2.1.4 and 2.1.5) dedicated to test campaigns performed on MCPs during the interference analysis. These key aspects raise the question of the relevance of tests executed on each CPU and the combinations of such tests to generate interferences.

This report proposes a classification of limits to interference analysis according to three criteria:

- Limits relative to the method—The method will not achieve its expected results, regarding safety aspects, complexity (i.e., combinatorial explosion of the number of test cases) or results' precision (i.e., oversizing margins because interference issues are not understood).

- Limits relative to the MCP—The method is correct, but the selected processor is not appropriate to implement this method.

- Limits relative to the industrial environment—The method is correct and the processor fits with method's requirements, but the industrial environment makes its implementation unfeasible; for instance, because of the lack of information on MCP components (e.g., interconnect, memory controllers) and/or applicative software.

Finally, this report proposes to illustrate the limits of a method contributing to interference analysis by driving a test campaign. This method aims at taking into account a restricted set of applicative profiles supported by a platform provider to provide tight interference penalties, this set being possibly extended during the whole life of equipment.

# 2 Limits to interference analysis

The notion of interference analysis was developed in the white paper [2] as a means to assess and justify the performance degradation of an avionics platform with regard to embedded software. This performance degradation is expressed as an "interference penalty" applied to the WCET of each application evaluated separately; therefore, the objective of interference analyses is twofold. It produces a performance evaluation used by an integrator to size margins, but it also introduces some arguments that will be used in safety analyses so as to achieve certification.

As detailed in reference [3], an interference analysis cannot aim at being fully exhaustive on COTS MCP. The number of test cases on an MCP is so significant that no one, even the chip manufacturer, is capable of testing all configurations.

The interference analysis can be seen as a way to drive offline analyses/test campaigns within acceptable time and costs. This allows performance overhead to be correctly assessed and provides evidence that stop criteria are reached. These criteria have to be agreed to at an early stage of the certification process as an activity of safe design, whereas the resulting test campaign deals with safety assessment.

Deciding on an interference analysis method, including the test methodology and its associated stop criteria must be performed carefully because the resulting test campaign may not be capable of achieving its objectives. The purpose of this section is to provide a generic classification of limits to interference analysis. It is divided into two subsections: section 2.1 introduces key aspects constituting an interference analysis, and section 2.2 illustrates limits on interference analysis on these key aspects.

## 2.1 Key aspects of interference analysis

To show the limits of interference analysis, a set of key aspects is introduced that may be detailed by an applicant at an early stage of the certification process. These key aspects are provided here as examples and should not necessarily correspond to separate entries in a certification plan; however, they raise questions that remain relevant to be addressed and agreed to with certification authorities at an early stage of an equipment development.

### 2.1.1 Hypotheses conditioning trustworthiness in an interference analysis

As previously stated, an interference analysis method drives analyses and test campaigns performed by the applicant on an MCP, but it also provides arguments to defend safety analyses during certification.

In safety analyses, interference analysis plays a role similar to WCET computation. It turns a source of risk into another source of risk that is hopefully easier to assess. More precisely, an applicant not performing an interference analysis faces the risk of missing deadlines in safety critical software because of unexpected/misunderstood interferences. Conversely, an applicant performing an interference analysis will be able to explain and cover performance issues on embedded software due to interferences, provided that the validity hypotheses of the method used are met.

One important aspect of interference analysis is to clarify the hypotheses under which the method's results can be trusted. The applicant should assess the validity of such hypotheses so as to conduct safety analyses at equipment level.

As an example, one approach developed and discussed in reference [3] relied on the assumption that the behavior of an MCP is not chaotic. This means the processor's behaviors are considered to have a non-null surface, so that they can be reached during close tests—the notion of "closeness" being defined by the applicant. Consequently, for a given set of configurations that are close enough, the applicant can expect to observe close behaviors and, therefore, similar levels of interferences, unless there is a mode change. This mode change would be observed by a discontinuity in interference level.

### 2.1.2 Range of conclusions from interference analysis

An interference analysis will provide interference penalties, which are engagements supported by a platform provider and are taken by an integrator to add safety margins on software WCET.

Whereas having a set of interference penalties is sufficient for integration, it is insufficient for safety assessment. The interference analysis method needs to be accompanied by argumentation that the applicant trusts these penalties; therefore, the question is about the way to define the range of conclusions derived from an interference analysis.

In the example developed in reference [3] and recalled in section, an example of conclusion is proposed. It is based on the notion of singularity, which consists in close discontinuities in the MCP behavior and, therefore, in observed interference levels. Informally, singularities correspond to isolated behaviors of the processor that may not be covered by tests and constitute

a feared event. In this example, the interference analysis would not conclude on the absence of singularities, but would provide a bound on their surface, which can be reused in a safety analysis and adjusted according to the equipment criticality level.

### 2.1.3 Definition of supported applicative profiles on the MCP

As explained in previous section, interference penalties are performance-related engagements taken by an applicant on an avionics platform embedding an MCP. However, such engagements may be conditioned by restrictions or hypotheses applied to embedded software, especially an applicative one and the way it uses hardware resources. The penalties and engagements constitute the supported applicative profiles for the MCP.

This key aspect is not mandatory. For instance, it may be decided that the set of relevant configuration parameters on the processor are sufficient to drive the interference analysis, the results of which would be valid for any applications. Such a configuration would minimize the impact of sources of non-determinism and the number of interference paths to cover, and finally cover them with worst-case scenarios. A rationale should be provided that these scenarios meet the "worst-case" and should be defended.

The applicative profiles may also be seen as a concept that will be continuously refined during the equipment's development, as long as the software development is getting closer to its final version or when targeted software is not known with a good level of detail by the platform provider (e.g., on IMA platforms). This concept may also be extended during the equipment's lifespan (e.g., when new software has to be deployed on the MCP platform). From this point of view, defining an MCP applicative scope can be seen as a prediction of the future needs of hardware resources by applicative software. The interference analysis will figure out the interference penalty while using hardware resources in a similar way.

### 2.1.4 Justification of individual test scenarios

This key aspect aims at justifying the relevance of the tests that will be deployed on each core of the MCP to generate interferences. The main reason is the extreme complexity of a test space that makes any exhaustive test campaign unpractical; therefore, only a subset of all possible configurations will be covered. Any way to justify a given set of test scenarios rather than another can be proposed, even randomly generated tests.

As an example, report [3] proposed to define and apply a metric on test scenarios, which would detail how much a configuration is close to another one. This metric enables the definition of a

notion of coverage with a given granularity over the test space, so that a threshold can be agreed to with certification authorities.

### 2.1.5 Selection of concurrent tests

This key aspect addresses the test campaign that consists in running test scenarios in parallel to measure the performance overhead introduced by interferences. The number of potential combinations can quickly become significant, so a selection is mandatory. This selection has to be justified.

Reference [3] detailed as an example the notion of stop criteria to justify the following:

- The decision to cover a more or less exhaustive subset of interference paths on the MCP.

- The decision to cover a more or less exhaustive subset of hardware configurations within a given interference path.

### 2.1.6 Evidence collection

The previous key aspects dealing with MCP's scope and the test campaign, both on the CPU-per-CPU and the concurrent aspects, were tackling design issues and safety. This key aspect deals with the safety assessment: Evidence has to be provided to the certification authorities that the test campaign has been handled according to the previously agreed parameters.

One goal is to define relevant indicators that have the following good features:

- Communication with certification authorities is limited to only significant information.

- The indicators remain independent from the MCP's architecture so that they can be reused in several certification projects.

- The indicators are adaptable to different criticality levels.

These key aspects do not constitute guidance or recommendation but have to be considered as a set of questions that may be legitimately raised during the development of a certified platform embedding an MCP. The purpose of these key aspects is to show the limits of interference analyses in the sense that under some conditions, some of these questions may become very hard to address.

## 2.2 Classification of interference analysis limits

The classification of interference analysis limits is proposed in this report according to the following aspects:

- Limits relative to the methods—These mostly theoretical limits are to be considered whatever the targeted equipment and the MCP. A deep adaptation of the method is required, or limitation may appear in the criticality level that can be reached.

- Limits relative to an MCP chip—These limits correspond to the situation for which an interference analysis method is suitable but cannot be deployed properly on a given MCP. Such limits may be tackled at an early stage by taking them into account during the MCP selection, or by adapting the method to fit the MCP characteristics.

- Limits relative to the industrial context in which the MCP is used in equipment—These limits correspond to configurations in which an interference analysis method fits the selected MCP but cannot be deployed properly because of the constraints introduced by the industrial environment (e.g., the restriction of information communication).

### 2.2.1 Limits intrinsic to interference analysis methods

Interference analysis methods are still a research topic; therefore, no consensus method, or family of methods, has emerged in the state-of-the-art yet. As a result, an interference analysis method might be proposed even if some of its aspects have not been experienced up to a high technology readiness level.

As previously explained, interference analyses play a role not only in performance assessment, but also in argumentation for safety analyses. Limits of an interference analysis method appear when one of these two objectives has not been clearly defined, or when both objectives are tackled in an unbalanced manner. Table 1 discusses some of these limits with regard to the key aspects introduced in section 2.1.

| Key aspect      | Method specific limits                                                                                                                                                                                                                                                                                                                                                         |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Trustworthiness | When an interference analysis method targets only performance assessment,<br>with a limited focus on argumentation for safety analyses, trustworthiness<br>hypotheses may not be expressed clearly, or may be defined in a way that<br>makes them difficult to verify. When this is the case, it adds a significant<br>complexity to the safety analyses performed on the MCP. |

| hypotheses      | An interference analysis method is likely to be refined all along the equipment's development. However, such a refinement might have a negative impact on trustworthiness hypotheses. The main risk here is to discover new hypotheses late in the interference analysis implementation, so that the method becomes irrelevant.                                                |

Table 1. Summary of key aspects and limits of associated methods

| Key aspect                           | Method specific limits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      | Having a clear understanding of the conclusions driven by an interference<br>analysis is necessary to be able to tackle it correctly from a safety point of<br>view.                                                                                                                                                                                                                                                                                                                                                            |

| Range of conclusions                 | Similarly to the previous key aspect (trustworthiness hypotheses), an interference analysis method has to be defined so that the focus is balanced between performance assessment and justification of this assessment for safety. Therefore, the conclusions of an interference analysis need to be understood in a safety context and be practical for use in a safety analysis. This entails a risk of not clearly defining these conclusions, or degrading them for as long as the interference analysis gains in maturity. |

|                                      | It is preferable that an interference analysis method relies on detailed<br>investigation on which levelis adjustable according to the criticality of the<br>targeted equipment. The same expectation applies to the range of conclusions<br>of an interference analysis.                                                                                                                                                                                                                                                       |

|                                      | An applicative profile can be considered as an abstraction of future applicative software, which may not be fully known during platform development. This key aspect is optional, in that a platform provider may decide to target any kind of application, with the risk that the resulting interference analysis becomes significantly complex to perform on a given MCP.                                                                                                                                                     |

|                                      | When the platform provider decides to restrict the scope of its platform with<br>applicative profiles, the issue of defining the profiles has to be addressed<br>carefully. These profiles describe the way applications use hardware<br>resources, so that the interference analysis can be performed while taking these<br>profiles into account. This introduces the risk that this abstraction:                                                                                                                             |

| Supported<br>applicative<br>profiles | • Is defined in a way too restrictive with regard to the software's actual behavior (i.e., it carries too much information so that an interference analysis would be valid only in specific cases, for instance in specific execution paths inside an application). Therefore, the interference analysis would have to consider too many applicative profiles to be sustainable on a real equipment.                                                                                                                            |

|                                      | • Requires modifications in the applications, so that only an instrumented code would be evaluated with respect to interference-related issues.                                                                                                                                                                                                                                                                                                                                                                                 |

|                                      | Requires information that cannot be observed on a real application without<br>being heavily intrusive in an application's execution flow (e.g., by suspending<br>it with instrumentation frameworks). In this case, the interference levels would<br>be irrelevant.                                                                                                                                                                                                                                                             |

| Key aspect                     | Method specific limits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Justification of               | Test campaigns seem unavoidable to perform an interference analysis on a complex COTS MCP, even if they do not constitute the sole investigation means, and would benefit from alternative methods (e.g., involving static analysis techniques).                                                                                                                                                                                                                                                                                                                                                                  |

|                                | Individual tests to be deployed on one CPU and then run in parallel with other tests will be developed with an objective of stressing some hardware resources (e.g., main memory, shared caches, on chip networks, I/O). They constitute a test suite that will be used during interference analysis.                                                                                                                                                                                                                                                                                                             |

| test scenarios on<br>each core | One risk is to accumulate many test cases without a clear understanding of<br>their added value within the test suite. Therefore, this suite could be extended<br>infinitely, whereas the applicant would not detect that additional tests are<br>useless. The consequence would be an interference analysis that is periodically<br>extended for a short duration to run additional test cases (i.e., there is a risk<br>that the interference analysis never produces satisfactory results regarding the<br>coverage of hardware behaviors by tests because the notion of coverage is not<br>properly defined). |

| Selection of concurrent tests  | Individual test cases, deployed CPU by CPU, constitute test suites. There may<br>be one test suite per CPU or test suites used on several CPUs. To generate and<br>measure interferences, test cases will be picked inside test suites, deployed and<br>run in parallel, so that their execution time's overhead due to interference will<br>be measured.                                                                                                                                                                                                                                                         |

|                                | Similar to test suites' constitution (see below), the selection of test cases to be<br>run in parallel is a difficult problem because all combinations cannot be<br>covered; therefore, only a subset of all combinations will be tested. The<br>question of the added value of a new combination with regard to the already<br>tested ones needs to be understood by the applicant. The risk is the same as for<br>individual tests constitution: performing an endless test campaign.                                                                                                                           |

|                                | The interference analysis will involve one or more test campaigns, possibly<br>generating a significant amount of data on the measured interference levels,<br>and the correct execution of the test campaigns. These data cannot be injected<br>"as is" in a certification report. Instead, they have to be summarized so that<br>only significant information is exchanged with certification authorities.                                                                                                                                                                                                      |

| Evidence<br>collection         | One risk associated with interference analysis is to launch test campaigns without clarifying the way test results will be processed and what kind of information will be significant.                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                | Moreover, when several investigation methods are used (e.g., test campaigns<br>and static analyses), the correlation between each result benefits from being<br>explained at an early stage of the interference analysis, so that the contribution<br>of each method to the final results is clarified.                                                                                                                                                                                                                                                                                                           |

### 2.2.2 Limits relative to MCP chips

This section considers an interference analysis method that has been correctly defined and is being implemented on an MCP chip. The limits relative to the MCP component, as presented in table 2, are defined as implementation limits because of its intrinsic characteristics. Therefore, such limits may have significant consequences when they are discovered at an advanced stage of the equipment's development, and may entail iterations in component selection, with significant extra-costs.

Note: This is a focus on interference analysis only so that the limits do not deal with complex COTS issues for which literature exists.

| Key Aspect                     | Limits Relative to MCP Component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Supported applicative profiles | <ul> <li>An applicative profile is an abstraction of the way embedded software will use shared resources on the MCP, so that test campaigns focus on a set of "supported" applicative profiles. This means that a toolset has to be developed to determine, from a given application, to which applicative profile should be referred.</li> <li>A possible limitation of this toolset is a dependency to specific hardware features that are not implemented on a given MCP. Some monitoring and instrumentation features may be required on the MCP. Examples of such features are:</li> <li>Low-latency breakpoint insertion capability to plug external debuggers.</li> <li>Hardware performance counters. For instance, most CPUs used in MCP provide a couple of counters that can sample various hardware events. Additionally, most MCPs implement performance counters within shared resources, so that the multiplexed activities of each initiator (CPU or other master device such as DMA engine) can be sampled.</li> <li>Tracing capabilities, with more or less intrusiveness in hardware behavior of trace probes.</li> <li>An applicative profile could typically be defined with a limited dependency on hardware features, so that it could be implementable on several kinds of processors with an adjustable level of precision.</li> </ul> |

| Evidence collection            | Similar to supported applicative profiles, evidence collection may<br>require monitoring and/tracing capabilities from the MCP.<br>An MCP may not provide sufficient capabilities (e.g., by not<br>implementing enough performance counters), or may not provide such<br>capabilities at all. This may have an impact on the quality of the<br>evidence collected during the test campaign.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Table 2. Summary of key | aspect and MCP comp | ponent relative limits |

|-------------------------|---------------------|------------------------|

|                         |                     |                        |

### 2.2.3 Limits relative to the industrial context

This section details the limits of interference analysis relative to the industrial context. These key aspects are summarized in table 3. In this industrial context, the methods are correct and the MCP implements hardware features that meet the methods' requirements. The focus is to explore the potential limits introduced by the industrial context, and more precisely:

- The multi-actor aspects, which are central in IMA, and limits due to existing processes and information not being shared between actors.

- The concurrent development of hardware and software, in which software needs are not known at the early stages of hardware development, so that interference analysis has to be launched with partial information on applicative software.

| Key Aspect                                                   | Limits Relative to the Industrial Context                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Trustworthiness<br>hypotheses and<br>range of<br>conclusions | Specific information might be required to verify some hypotheses. This information is not available to the MCP platform provider because it is confidential.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                              | <ul> <li>Applicative profiles are a means to exchange information between:</li> <li>The platform provider, who has to drive the interference analysis according to the supported applicative profiles.</li> <li>The integrator, who has to consider which applicative profiles to refer to so as to obtain interference penalties and size margins.</li> <li>Possibly the application provider, who has a targeted applicative profile to cover.</li> </ul>                                                                                                                                                                           |

| Supported<br>applicative profiles                            | <ul> <li>These actors may or not belong to the same organization and apply an IMA process or not. Underlying risks are:</li> <li>Lack of information about applications, either because of the anticipation of their development (the integrator himself may not have a good overview of the applications being integrated until later in the development), or because of confidentiality.</li> <li>Lack of agreement between actors on the way applicative profiles are defined.</li> <li>Misunderstanding on the validity of applicative profiles, so that integration is performed on erroneous interference penalties.</li> </ul> |

Table 3. Summary of key aspects and limits relative to the industrial context

### 2.3 Synthesis

In section 2, the notion of interference analysis methods is structured from the basic assertions exposed in section 1.4. These methods are developed around six key aspects, one being optional. These aspects represent distinct stakes an applicant should explore. The proposed approach does not apply any constraint on the manner by which the applicant is performing such exploration nor on the manner in which the results of the exploration are reported to clarify the impact of such methods on safety analyses, test campaigns, and offline analyses.

Furthermore, the notion of limits to interference analyses is developed by listing conditions under which some of these key aspects might be difficult to fulfill, or be fulfilled but in an unsatisfying manner. These limits are classified as intrinsic to (1) the methods, (2) the MCP chip they are applied to, or (3) the industrial environment. Each class has various implications with respect to the method design or component selection.

Developing the notion of limits to interference analyses also highlights good properties the applicant can expect from an interference analysis method, namely:

- Providing interference penalties to be applied on the software's WCET and therefore on equipment's performances, and safety arguments substantiating these penalties, with a good balance between these two objectives.

- Being adjustable according to the equipment's criticality level and development stage, especially when considered at an early stage in which hardware and software building blocks have not achieved a good level of maturity.

- Being adjustable in reachable precision according to the MCP's hardware features, especially monitoring and tracing capabilities.

- Being adaptable to an industrial context involving multiple industrial actors, each having a partial visibility on hardware and software involved in the equipment. One example of such a context is IMA.

# 3 Application of proposed method and associated limits

A common, quick but imprecise approach to tackle interference issues consists in stressing each interference path up to the highest possible level of workload to maximize interferences, measure them, and determine interference penalties. The highest penalty possible is the interference penalty on the platform (i.e., interference penalties are obtained by denial-of-service attacks).